基于表面贴装技术工艺数据的印刷电路板功能评估

论文相关信息

本文内容取自[1]。

研究背景与意义

功能测试作为印刷电路板(PCB)生产的最后一道工序,是 PCB 生产过程的重要组成部分。功能测试通过测试机台模拟 PCB 的运行环境,使其在各种设计状态下工作,从而检查 PCB 在不同设计状态下的性能。通过高效的功能测试,可以避免将有缺陷的 PCB 组装到电子设备中,从而降低维修成本。

工厂中主要采用的固定测试策略存在测试时间过长和测试成本过高的问题,需要进行优化。通常情况下,固定测试策略将功能测试项目分为必测项和选测项。对于必测项,所有 PCB 都必须进行测试;对于选测项,将按照预定比例随机选择 PCB 进行测试。例如,一家典型的笔记本电脑制造商可以在十几秒内下线一批 PCB,而测试PCB 的必测项大约需要几十秒,选测项则需要几分钟。为了防止 PCB 积压,必须添加大量测试机台(每台成本超过 10000 美元)以便同时测试大量 PCB。此外,由于选测项的测试是随机抽取,这就可能导致部分存在潜在缺陷的 PCB 被漏检,使得有问题的产品流入后续生产环节,增加了产品整体的质量风险。因此,固定测试策略会导致成本显著增加,需要被优化。

由于功能测试的细节属于商业机密,关于测试策略调整的学术研究较为缺乏。我们的研究团队与一家笔记本电脑制造商合作,首次完成了功能测试通用框架的数学建模[2],并提出了基于良率预测的测试项目选择 [3]、基于故障树分析和二元优化的功能测试成本降低 [4] 等解决方案。这些解决方案通过调整所选测试项目的测试比例,达到了减少测试时间和降低功能测试成本的目的。然而,这些解决方案需要收集大量的历史功能测试数据。因此,它们仅适用于 PCB 大规模生产的情况,并且测试机台的测试项目需要根据所选测试项目频繁设置。

由于PCB 生产过程具有高度的耦合性,每个生产步骤都可能对 PCB 的功能产生影响。因此,一个自然的想法是通过表面贴装技术(SMT)工艺数据来评估 PCB 的功能,并重点测试可能存在缺陷的 PCB。这种方法不需要收集大量的 PCB 功能测试数据,也不需要修改测试机的设置,并且可以节省更多的测试时间和测试成本。

本文工作

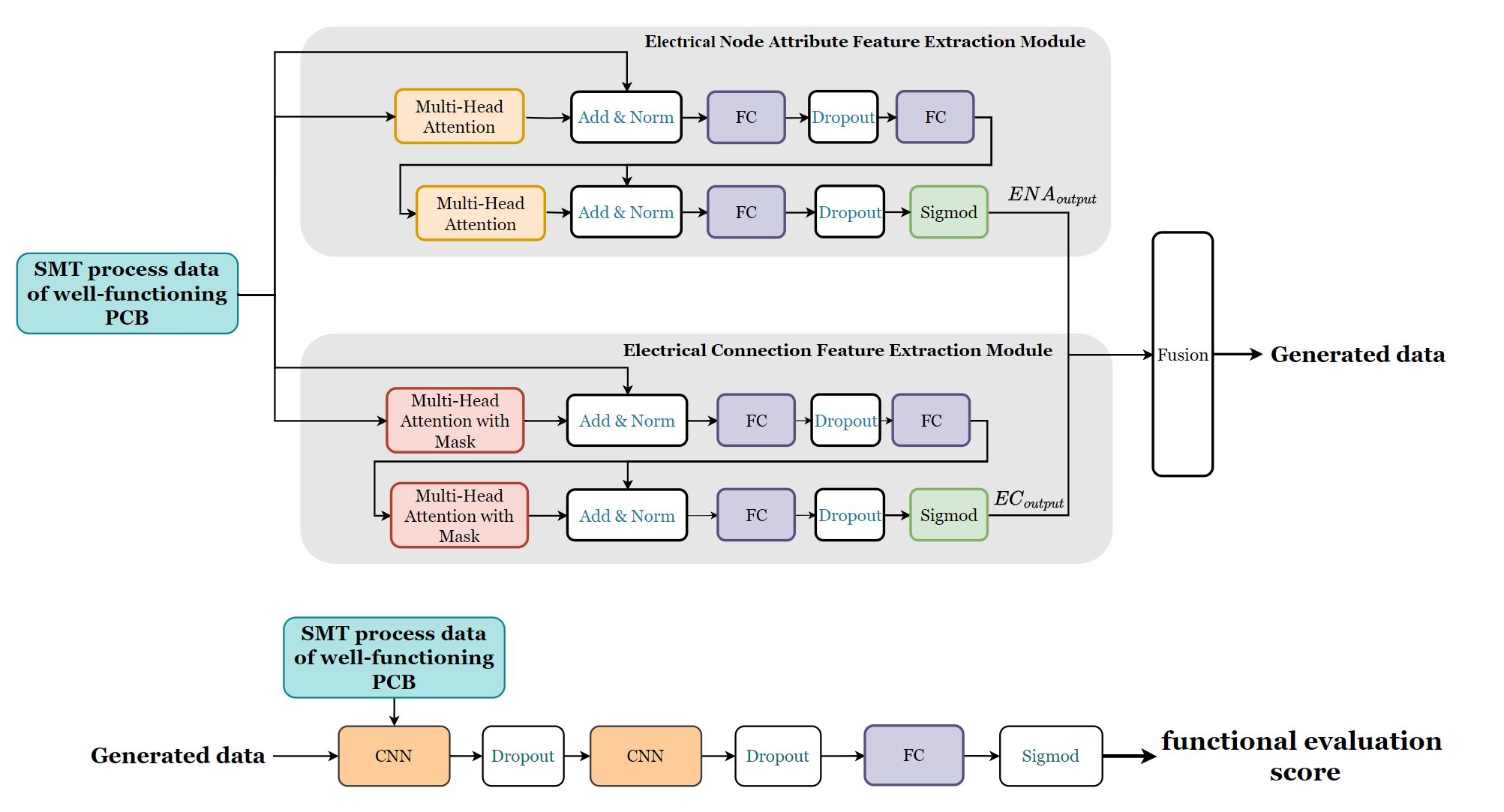

本文提出了一种基于电路布局的生成对抗网络方法(CL-GAN),用于评估 PCB 的功能。生成对抗网络(GAN)可以对功能正常的 PCB 的生产数据分布进行建模,从而有效地识别出与该数据分布不一致的异常值 —— 缺陷PCB。首先,我们在生成器部分设计了两个模块。电气节点属性特征提取模块用于提取 PCB 电气路径中关键节点的质量属性之间的特征。对于电气连接特征提取模块,我们设计了一种基于 PCB 电路布局的掩码机制,以反映电气连接关系,使模型能够对 PCB 的电路结构进行建模。然后,我们融合两个模块的输出,以确保生成的数据更加真实。接下来,我们训练判别器。最后,使用训练好的判别器来评估 PCB 的功能。

CL-GAN 的整体结构如图 1 所示。

图1 方法结构图

(一)电气节点属性特征提取模块

为了更好地对 PCB 电气路径中关键节点的质量属性进行建模,我们设计了一个电气节点属性特征提取模块。该模块使用 Transformer 来提取电气节点的属性特征。凭借其强大的注意力机制,它可以有效地捕捉数据中各种属性之间的复杂关系。

(二)电气连接特征提取模块

在对 PCB 的电气连接关系进行建模时,直接使用多头注意力机制可能无法捕捉电路中复杂的元件互连关系,从而无法对实际电路结构进行建模。因此,我们设计了一种基于电路布局的掩码机制,以反映节点位置和电路结构。这种机制通过屏蔽没有电路连接的节点之间的注意力计算,突出电路结构,确保模型在处理数据时能够准确地对电路结构进行建模,专注于节点之间的电气连接关系。具体而言,我们根据电路布局获取 PCB 的电路结构。然后,基于电路结构,我们保留有电路连接的节点之间的注意力。这样,相互之间存在注意力连接的节点就是存在电路连接的,并且具有实际的物理意义。掩码矩阵\(A\)可以通过以下公式获得:

$ A_{ij}=\begin{cases}1, & (i, j) \in \mathbb{K} \ 1e-9, & others\end{cases} $

其中,\(i\)、\(j\)代表第\(i、j\)个焊点,\(\mathbb{K}\)是一个存储电路连接焊点对的集合。

此时,注意力公式应更改为:

$ Attention = softmax((\frac{QK^T}{\sqrt{d_k}})V+log(A)) $

通过使用基于电路布局设计的掩码,可以反映电气连接关系。这样的掩码为模型提供了一个线索,引导它专注于真正重要的电路结构,从而提高模型对 PCB 工艺数据的理解能力。

(三)判别器结构

判别器结构如图所示,主要由卷积神经网络(CNN)组成。卷积层负责提取局部特征,这使得判别器能够有效地捕捉输入数据的多层次特征,并提取细微差异。经过 Sigmod 处理后,输出功能评估分数,以有效地区分真实样本和假样本。随着训练过程的进行,生成器不断调整参数,生成更接近真实的数据,而判别器则不断提高其判别能力。 在功能评估过程中,判别器会给训练过程中经常出现的功能正常的 PCB 数据更高的分数;而对于未见过的 PCB 缺陷数据,由于其特征与训练集中功能正常的数据有很大差异,判别器在处理此类数据时会给出较低的分数,从而实现 PCB 功能评估。

实验结果

实验使用从合作工厂自动化生产线收集的真实数据,并对数据进行归一化处理。实验采用准确率、F1分数评估CL-GAN性能,还提出成本差异公式衡量成本节省情况。 将CL-GAN与多种方法对比,CL-GAN准确率达到 97.99%,F1 分数为 0.6667。与合作工厂的方法相比,可以节省 96.64% 的测试时间和 64.77% 的总成本。

参考文献

- [1]Y. Kang, P. Bai, K. Wang, Y. Zhao, and S. Dong, “Modelling and Optimizing Motherboard Functional Testing in Laptop Manufacturing,” Journal of Systems Science and Complexity, Sep. 2024.

- [2]J. Li, Y. Zhao, and B. Liu, “Functional Evaluation for Printed Circuit Board Based on Surface Mount Technology Process Data,” in 2024 11th International Forum on Electrical Engineering and Automation (IFEEA), 2024, pp. 18–21.

- [3]Y. Zhao, S. Dong, Y. Kang, K. Wang, L. Chen, and P. Bai, “Prediction of Yield in Functional Testing of Motherboards in Laptop Manufacturing,” in 2024 14th Asian Control Conference (ASCC), 2024, pp. 1–5.

- [4]X. Zuo, K. Wang, Y.-B. Zhao, Y. Kang, and P. Bai, “Functional Test-Cost Reduction Based on Fault Tree Analysis and Binary Optimization,” in 2024 43rd Chinese Control Conference (CCC), 2024, pp. 6905–6910.